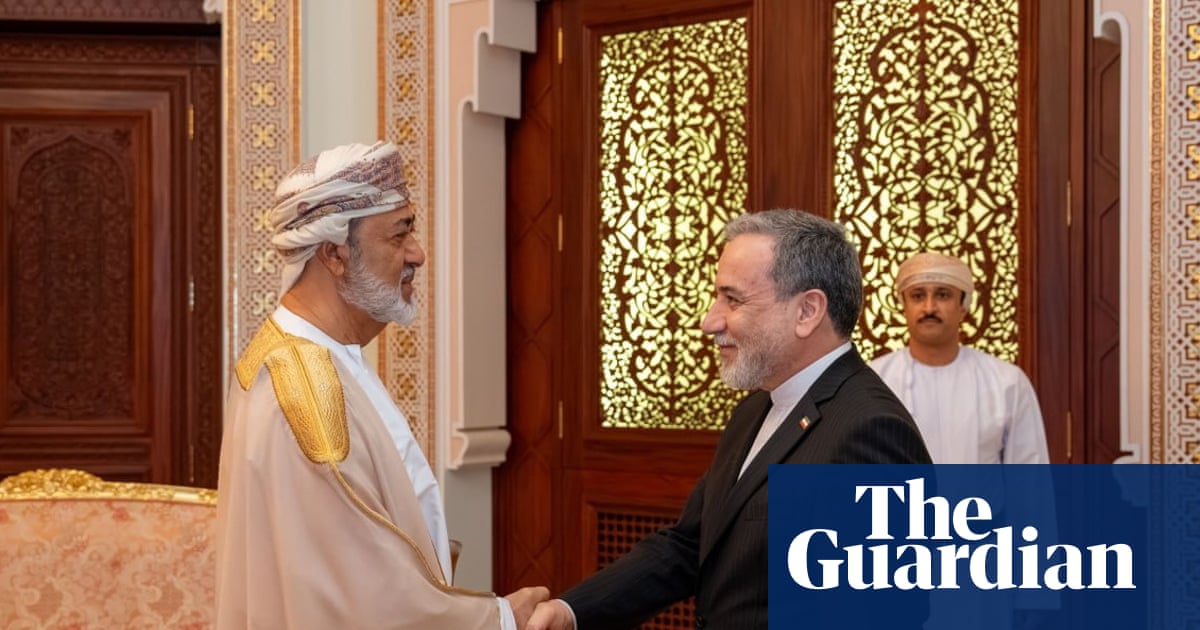

Stalemate in US-Iran Diplomacy: No Progress in Middle East Peace Efforts as Tensions Persist

As diplomatic channels between Washington and Tehran remain frozen, the stalemate over Iran’s nuclear program and regional influence is triggering ripple effects across global energy markets, with oil prices climbing ... Read More