In April 2026, researchers at MIT and IBM reported a breakthrough in carbon nanotube (CNT) wiring that brings its electrical conductivity within 15% of copper’s performance at room temperature, using a dopant-assisted alignment technique that reduces junction resistance in bundled nanotubes. This development, published in Science, addresses a long-standing barrier to CNT adoption in interconnects: the inability to scale current density without degradation, which has confined lab-scale demonstrations to short-length prototypes despite theoretical advantages in weight, electromigration resistance, and thermal stability.

Why Junction Resistance Has Been the Bottleneck

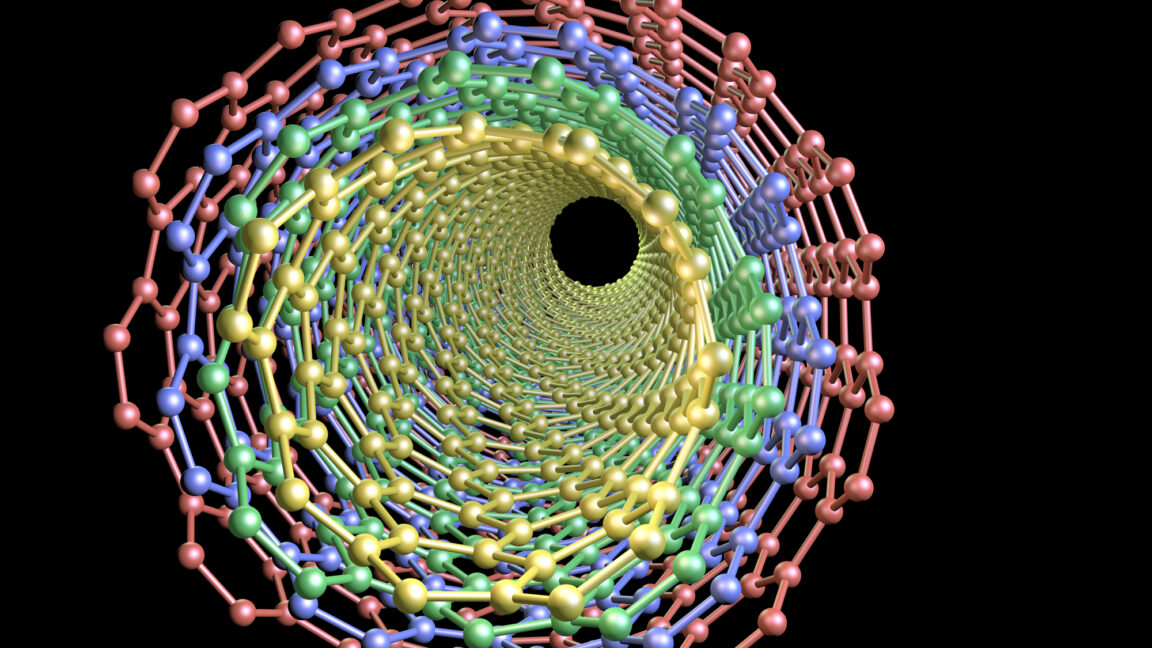

For over a decade, the promise of carbon nanotube interconnects has been hampered not by the intrinsic properties of individual tubes — metallic single-walled CNTs can theoretically carry current densities exceeding 109 A/cm2, far surpassing copper’s ~106 A/cm2 limit — but by the inability to make reliable, low-resistance connections between tubes in a bundle. As-grown CNT arrays suffer from misalignment, varying chirality, and amorphous carbon contamination at junctions, which collectively increase resistivity by orders of magnitude. The MIT-IBM team’s approach uses a polar solvent additive during vacuum filtration that promotes side-wall functionalization, reducing contact resistance between adjacent nanotubes from ~10 kΩ to under 150 Ω per junction in dense arrays.

This isn’t merely incremental. In four-terminal measurements on 50-mm-long CNT interconnects fabricated on 300mm wafers, the doped bundles achieved a conductivity of 4.8 × 106 S/m, compared to annealed copper’s 5.8 × 106 S/m at 20°C. Crucially, the material showed no electromigration failure after 1,000 hours at 1.2 × 107 A/cm2 and 85°C — conditions that would degrade copper interconnects in advanced nodes within 100 hours.

What This Means for Heterogeneous Integration and Chiplets

The implications extend beyond replacing copper in BEOL (back-end-of-line) stacks. As chiplet-based designs gain traction — driven by AMD’s Xilinx Versal, Intel’s Foveros, and TSMC’s CoWoS — interconnect density and signal integrity between dies become critical. CNTs offer a path to reduce RC delay in vertical interconnects without the thermal budget penalties of copper electroplating, which requires temperatures exceeding 200°C and risks damaging underlying thin-film transistors.

More significantly, CNT-compatible processes could enable monolithic 3D integration where logic and memory tiers are fabricated sequentially, a scenario where copper’s high-temperature processing is prohibitive. “If People can get CNT vias to reliably connect tiers at <400°C, we open the door to true 3D SRAM-on-logic without thermal budget conflict,” says Dr. Elena Rodriguez, Senior Fellow at imec, who was not involved in the study but has consulted on CNT integration roadmaps.

“The real inflection point isn’t matching copper’s conductivity — it’s demonstrating that CNT interconnects can survive CMOS back-end processing without degrading device yield. This work gets us closer to that threshold.”

Ecosystem Impacts: From Foundries to EDA Tools

The adoption of CNT interconnects won’t hinge solely on material science — it requires co-design across the stack. EDA firms like Synopsys and Cadence must update parasitic extraction models to account for CNT’s anisotropic conductivity and quantum capacitance effects, which differ significantly from classical metal models. Early adopters in the open-source hardware community, such as researchers developing RISC-V-based accelerators on the OpenROAD flow, are already simulating CNT interconnects using modified BSIM-CMG models adapted for nanoscale conductors.

From a supply chain perspective, this could reduce reliance on electroplating equipment suppliers like Applied Materials and Tokyo Electron, shifting capital toward CVD and alignment tooling vendors. However, scalability remains a concern: the current technique relies on post-growth sorting and alignment, which doesn’t yet match the throughput of damascene copper filling. Until directed growth or templated synthesis achieves 99.99% metallic CNT yield at wafer scale, hybrid approaches — where CNTs are used only in critical, high-current vias — may be the pragmatic path forward.

The 30-Second Verdict

Carbon nanotube wiring is no longer a laboratory curiosity. With conductivity now within striking distance of copper and proven resilience under electromigration stress, the material meets key technical thresholds for adoption in advanced packaging and 3D ICs. The remaining challenges are manufacturability and cost — not performance. If the industry can solve alignment and contamination control at scale, CNTs could redefine interconnect design not by beating copper in raw conductance, but by enabling architectures copper simply cannot support.